# Q7-BT Technical Reference

Oseven Computer On Module with Intel<sup>®</sup> Atom™ E3800 Series Processors

Manual Rev.: 2.1

7 □ □ □ ∨ □ N Revision Date: June 18, 2018

Part Number: 50-1Z202-1020

## **Preface**

#### Disclaimer

Information in this document is provided in connection with ADLINK products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in ADLINK's Terms and Conditions of Sale for such products, ADLINK assumes no liability whatsoever, and ADLINK disclaims any express or implied warranty, relating to sale and/or use of ADLINK products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. If you intend to use ADLINK products in or as medical devices, you are solely responsible for all required regulatory compliance, including, without limitation, Title 21 of the CFR (US), Directive 2007/47/EC (EU), and ISO 13485 & 14971, if any. ADLINK may make changes to specifications and product descriptions at any time, without notice.

#### **Trademarks**

Product names mentioned herein are used only for identification purposes and may be trademarks and/or registered trademarks of their respective companies.

## **Revision History**

| Revision | Date      | Description of Change(s)                                                                                                                                                                                                          |  |

|----------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1.00     | 9/21/2015 | Initial Release                                                                                                                                                                                                                   |  |

| 2.00     | 8/8/2016  | Added changes for A3 board revision                                                                                                                                                                                               |  |

| 2.1      | 6/18/2018 | Updated pin 3 of SW4 in Table 2-2 from "Not Connected" to "Selecting BIOS"; added note to pin 3 of SW4 to indicate BIOS_DISABLE# must be pulled low; added Figure 1-1 to Chapter 1; added Battery and Prop 65 warnings to Preface |  |

## © Copyright 2015, 2016, 2017, 2018 ADLINK Technology, Incorporated

This document contains proprietary information protected by copyright. All rights are reserved. No part of this manual may be reproduced by any mechanical, electronic, or other means in any form without prior written permission of the manufacturer.

#### **Audience**

This manual provides reference only for computer design engineers, including but not limited to hardware and software designers and applications engineers. ADLINK Technology, Inc. assumes you are qualified to design and implement prototype computer equipment.

ii Preface

#### **Environmental Responsibility**

ADLINK is committed to fulfill its social responsibility to global environmental preservation through compliance with the European Union's Restriction of Hazardous Substances (RoHS) directive and Waste Electrical and Electronic Equipment (WEEE) directive. Environmental protection is a top priority for ADLINK. We have enforced measures to ensure that our products, manufacturing processes, components, and raw materials have as little impact on the environment as possible. When products are at their end of life, our customers are encouraged to dispose of them in accordance with the product disposal and/or recovery programs prescribed by their nation or company.

Battery Labels (for products with battery)

#### California Proposition 65 Warning

WARNING: This product can expose you to chemicals including acrylamide, arsenic, benzene, cadmium, Tris(1,3-dichloro-2-propyl)phosphate (TDCPP), 1,4-Dioxane, formaldehyde, lead, DEHP, styrene, DINP, BBP, PVC, and vinyl materials, which are known to the State of California to cause cancer, and acrylamide, benzene, cadmium, lead, mercury, phthalates, toluene, DEHP, DIDP, DnHP, DBP, BBP, PVC, and vinyl materials, which are known to the State of California to cause birth defects or other reproductive harm. For more information go to www.P65Warnings.ca.gov.

## Conventions

The following conventions may be used throughout this manual, denoting special levels of information.

This information adds clarity or specifics to text and illustrations.

This information indicates the possibility of *minor* physical injury, component damage, data loss, and/or program corruption.

This information warns of possible serious physical injury, component damage, data loss, and/or program corruption.

iii Preface

## **Important Safety Instructions**

For user safety, please read and follow all **Instructions**, **WARNINGs**, **CAUTIONs**, and **NOTEs** marked in this manual and on the associated equipment before handling/operating the equipment.

- ▶ Read these safety instructions carefully.

- ▶ Keep this manual for future reference.

- ▶ Read the specifications section of this manual for detailed information on the operating environment of this equipment.

- ► Turn off power and unplug any power cords/cables when installing/mounting or un-installing/removing equipment.

- ▶ To avoid electrical shock and/or damage to equipment:

- > Make sure to use recommended voltage and power source settings;

- ▷ Always install and operate equipment near an easily accessible electrical socketoutlet;

- ▷ Secure the power cord (do not place any object on/over the power cord);

- Only install/attach and operate equipment on stable surfaces and/or recommended mountings; and,

- ▷ If the equipment will not be used for long periods of time, turn off the power source and unplug the equipment.

iv Preface

# **Table of Contents**

| Pr | Preface                                | ii |

|----|----------------------------------------|----|

| 1  | Product Overview                       |    |

|    | 1.1 Description                        | 1  |

|    | 1.2 Features                           | 2  |

|    | 1.3 Block Diagram                      | 3  |

|    | 1.4 Specifications                     | 4  |

|    | 1.4.1 Physical                         | 4  |

|    | 1.4.2 Electrical                       | 4  |

|    | 1.4.3 Environmental                    | 4  |

|    | 1.4.4 Mechanical                       | 5  |

|    | 1.4.5 Power                            | 6  |

|    | 1.4.6 Cooling                          | 6  |

|    | 1.5 Getting Started                    | 7  |

|    |                                        |    |

| 2  |                                        |    |

|    | 2.1 Major Components (ICs)             |    |

|    | 2.2 Connectors, Switches, and LEDs     |    |

|    | 2.3 Component Features                 |    |

|    | 2.3.1 CPU                              |    |

|    | 2.3.2 Memory                           |    |

|    | 2.3.3 eMMC NAND Flash                  |    |

|    | 2.3.4 SATA SSD (Solid State Drive)     |    |

|    | 2.3.5 SMBus Slave Addresses            | 14 |

| 3  | Interfaces                             | 15 |

|    | 3.1 18/24-Bit LVDS LCD                 | 16 |

|    | 3.2 HDMI or Display Port (DP)          | 16 |

|    | 3.3 Camera MIPI-CSI                    | 16 |

|    | 3.4 Audio (HDA)                        | 16 |

|    | 3.5 PCI Express (PCIe)                 | 16 |

|    | 3.6 Gigabit Ethernet                   | 16 |

|    | 3.7 USB Ports                          | 17 |

|    | 3.8 SATA                               | 17 |

|    | 3.9 I2C Bus                            | 17 |

|    | 3.10 SPI                               | 17 |

|    | 3.11 Serial (UART)                     | 17 |

|    | 3.12 SD/SDIO Interface                 |    |

|    | 3.13 eMMC Interface                    | 17 |

|    | 3.14 LPC Debug Interface               |    |

|    | 3.15 MIPI CSI Camera Interface         |    |

|    | 3.16 Qseven Interface Signals          |    |

|    | 3.17 Debug (DB40) Connector Signals    |    |

|    | 3.18 MIPI CSI Camera Connector Signals |    |

| Utilities                           | 27       |

|-------------------------------------|----------|

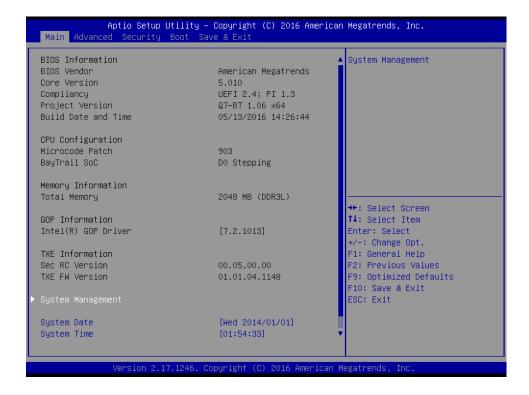

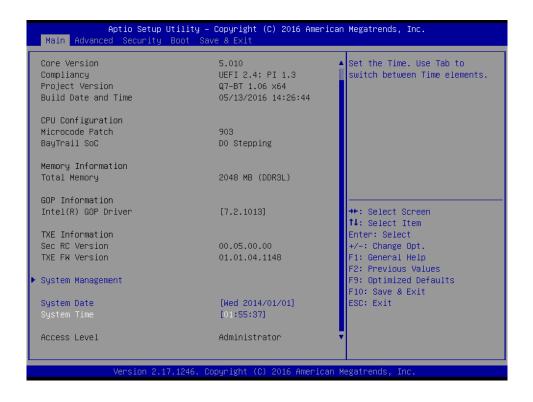

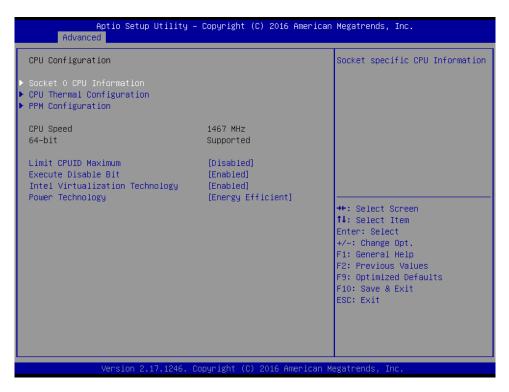

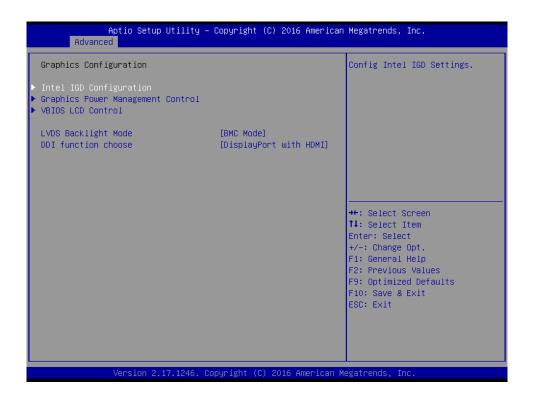

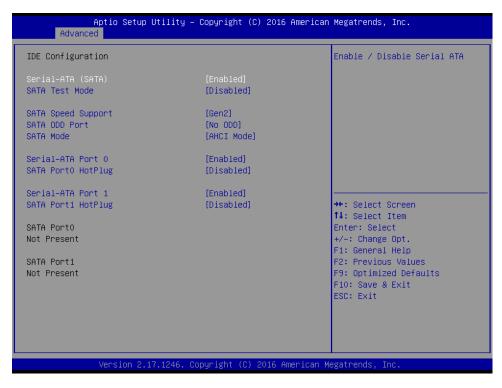

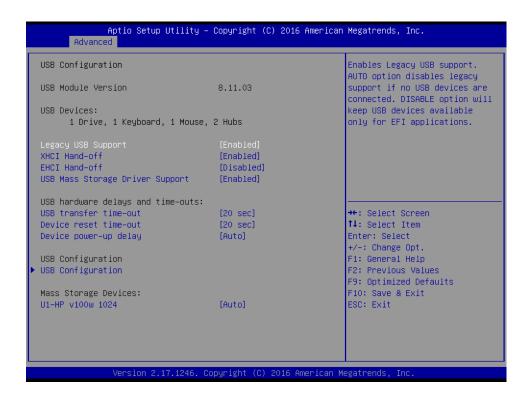

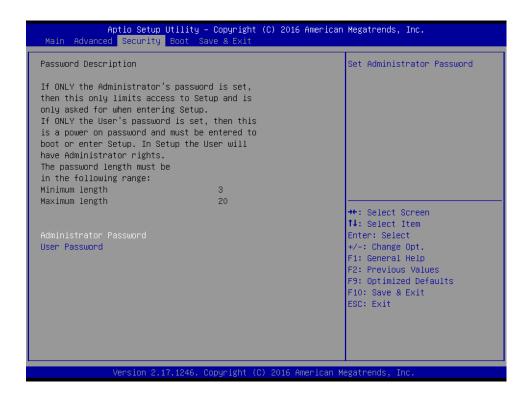

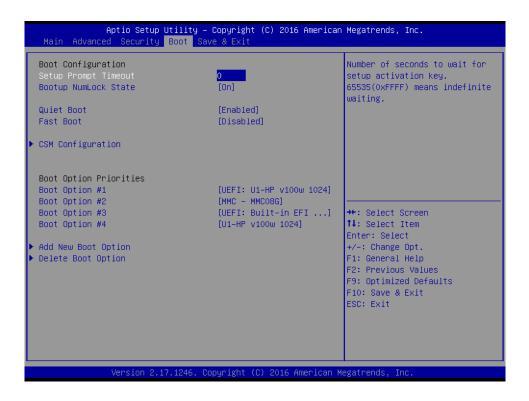

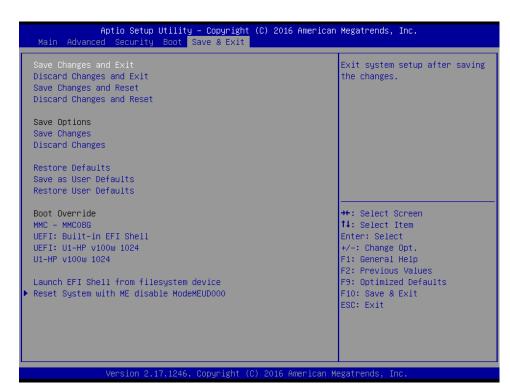

| 4.1 BIOS                            | 27       |

| 4.1.1 Configuring the BIOS          | 27       |

|                                     |          |

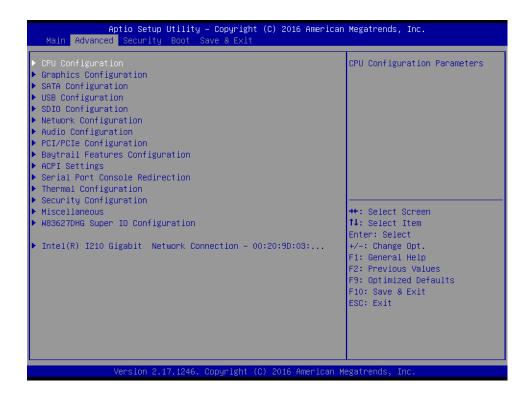

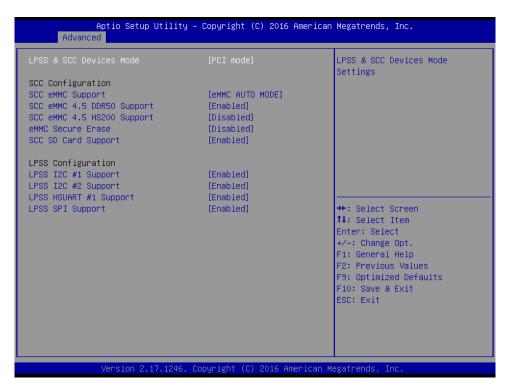

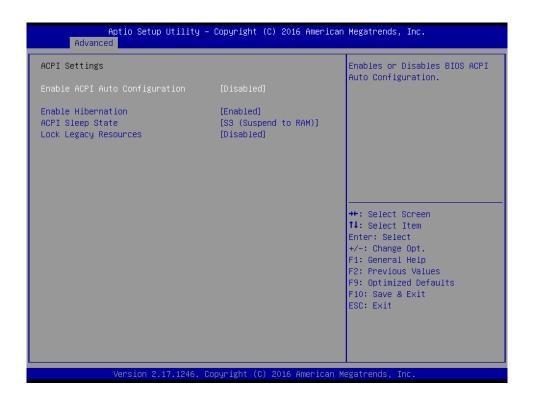

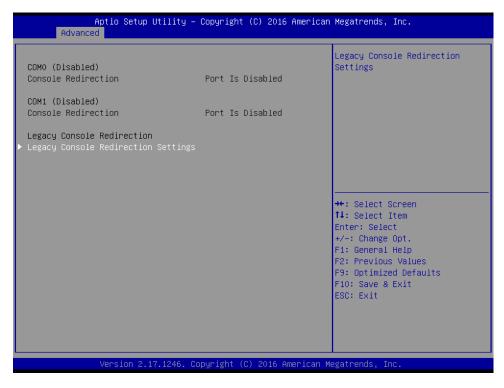

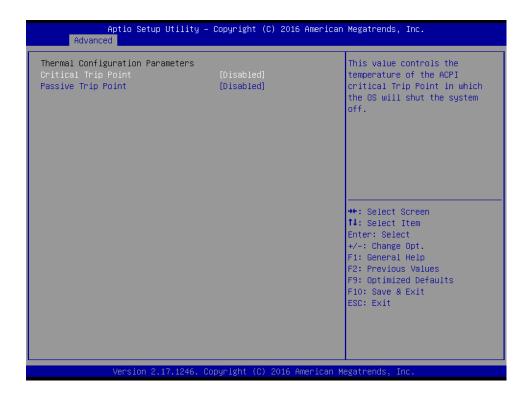

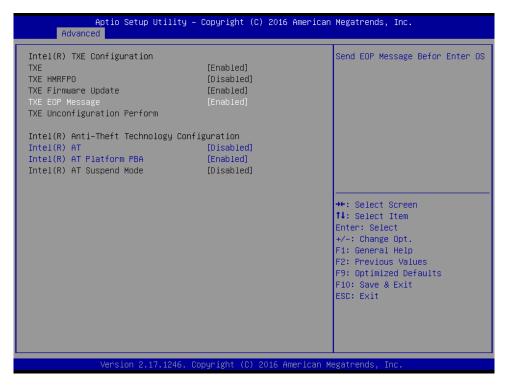

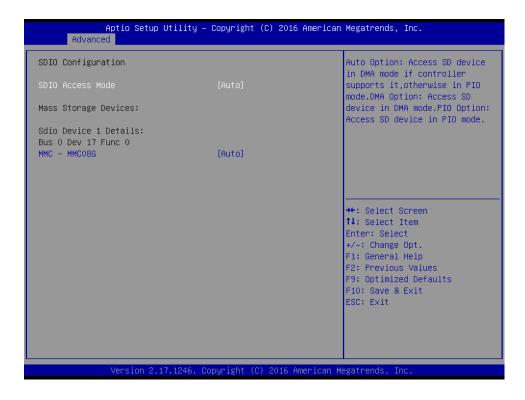

| 4.1.3 Advanced Settings screen      | 29       |

|                                     |          |

|                                     |          |

| 4.1.6 Save & Exit screen            | 38       |

| 4.2 SEMA functions                  | 39       |

| 4.2.1 Board Specific SEMA functions | 40       |

| 4.3 Watchdog Timer                  | 41       |

| 4.4 Temperature Sensors             | 41       |

|                                     |          |

| Appendix A Technical Support        | 43       |

|                                     | 4.1 BIOS |

## 1 Product Overview

## 1.1 Description

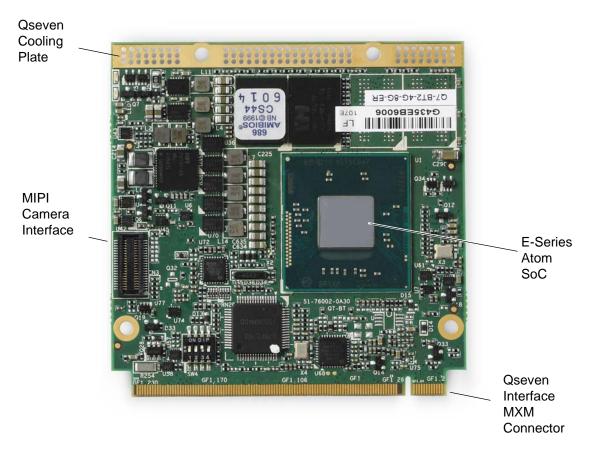

The Q7-BT Computer-On-Module (COM) combines the Qseven<sup>®</sup> 2.0 standard with the Intel<sup>®</sup> Atom<sup>™</sup> E3800 series System-on-Chip (SoC), providing an ideal solution for mid-range power and high, pin/area density requirements. The module provides the high integration, high performance, low power, and ruggedness favored by Internet-of-Things (IoT) applications such as retail transactional clients, digital signage, and in-vehicle infotainment systems.

The Qseven form factor affords a more compact profile and footprint than the other COM platforms. With mechanical dimensions as small as 70mm width, 70mm length, and 2.3mm of overall height, Qseven ranks as the smallest COM standard currently available.

The Q7-BT module utilizes the E3800 SoC for contemporary, high-bandwidth interfaces such as PCI Express, USB, Gigabit Ethernet, SATA, and HD Audio. The module generates its own LVDS, TMDS, and DisplayPort video signals using DDI output from the SoC.

A series of optional eMMC devices offers up to 64GB of on-board NAND Flash storage with an MMC interface, and an optional SATA, Solid State Drive (SSD) provides up to 64GB of on-board NAND Flash storage. Two SPI Flash chips implement a fail-safe BIOS, allowing the user to boot the module even if current BIOS settings have corrupted the system.

Under the management of the BMC chip (Board Management Controller), the SEMA utility (Smart Embedded Management Agent) provides system control, security, and failure protection—counting, monitoring, and measuring hardware and software events, and using the SMBus to send corrective commands to the SoC. The optional SEMA Cloud utility not only controls local events on the module but system client events on the IoT.

Figure 1-1: Overview of Q7-BT with Intel E-Series SoC

#### 1.2 Features

#### ▶ CPU

Intel® Atom™ E3800 Series, single, dual, or quad-core SoC (System-on-Chip) with integrated memory, graphics, and I/O. See the E3800 data sheet at the Intel website.

- ▷ E3826 7W TDP, 1.46GHz Dual-Core/1066 MT/s with Gfx 533/667 MHz, Turbo

- ▷ E3825 6W TDP, 1.33GHz Dual-Core/1066 MT/s with GFx 533/533 MHz, Turbo

- ▷ E3815 5W TDP, 1.46GHz Single-Core/1066 MT/s with Gfx 400MHz, Non-Turbo

- E3805 3W TDP, 1.33GHz Dual-Core/1066 MT/s without GFx

#### ▶ Memory

- > Single channel

## ► Expansion

#### ► SATA

#### ▶ USB

- ▷ One USB 3.0 port

#### ▶ Ethernet

## Serial UART

#### ▶ 12C

- > One I2C bus

- ▷ One SMBus

#### ▶ SPI

## ▶ Video

- Display Port/HDMI

#### ▶ Audio

▷ One HDA (High Definition Audio) interface

#### ► CSI/MIPI Camera

- ▷ One front-end interface for 3 sensors

- ▷ Capacity for acquiring 1 stream simultaneously from each sensor

#### Storage

- ▷ One optional eMMC NAND

- ▷ One optional SATA SSD

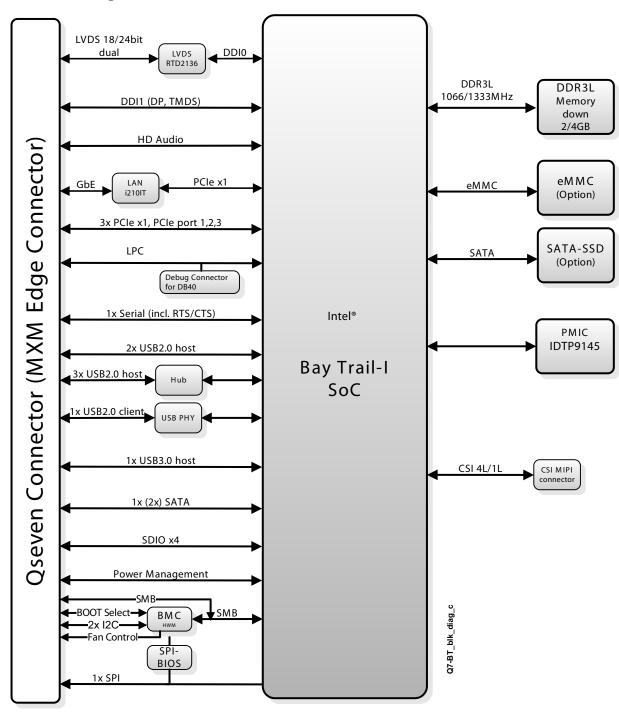

## 1.3 Block Diagram

Figure 1-2: Module functional block diagram

## 1.4 Specifications

## 1.4.1 Physical

Table 1-1 lists the physical dimensions of the module.

Table 1-1: Weight and Footprint Dimensions

| Dimension        | Measurement                              | Overall height is measured from the upper board                                                                                           |

|------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Weight           | 0.025 kg<br>[0.09 kg with heat spreader] | surface to the top of the highest permanent component on the upper board surface. This measurement does not include the cooling solution. |

| Height (overall) | 2.29mm                                   | 3                                                                                                                                         |

| Board thickness  | 1.27mm                                   |                                                                                                                                           |

| Width            | 70.00mm                                  |                                                                                                                                           |

| Length           | 70.00mm                                  |                                                                                                                                           |

## 1.4.2 Electrical

Table 1-2 specifies the electrical characteristics of the module.

**Table 1-2: Electrical Specifications**

| Parameter     | Value                                                                                    |  |  |

|---------------|------------------------------------------------------------------------------------------|--|--|

| Voltage Input |                                                                                          |  |  |

| Standard      | ► +5 V DC, +/-5%, =/- mV ripple                                                          |  |  |

| Standby       | <ul> <li>+5 V standby +/-5%, =/- mV ripple (only needed<br/>for suspend mode)</li> </ul> |  |  |

| RTC           | ► 3.0V, 2.0V to 3.3V (battery), +/-20mV ripple                                           |  |  |

| Power States  | ► C1-C6, S0, S1, S4, S3, S5, S5 ECO mode (wake on USB S3/S4, WOL S3/S4/S5)               |  |  |

## 1.4.3 Environmental

Table 1-3 defines the environmental conditions under which the module is qualified to operate and to be stored.

Table 1-3: Temperature, Humidity, and Pressure

| Parameter     | Temperature                                   |  |  |

|---------------|-----------------------------------------------|--|--|

| Temperature   |                                               |  |  |

| Standard      | ▶ 0°C to +60°C                                |  |  |

| Extended      | ► -40°C to 85°C                               |  |  |

| Storage       | ► -55°C to 85°C                               |  |  |

| Humidity      |                                               |  |  |

| Operating     | ▶ 5% to 90% relative humidity, non-condensing |  |  |

| Non-operating | ▶ 5% to 95% relative humidity, non-condensing |  |  |

Table 1-4 presents the average times between system failures.

Table 1-4: Mean Time Between Failures

| Parameter    | Value                                      |

|--------------|--------------------------------------------|

| MTBF at 40°C | 278,930 hrs (according to MIL calculation) |

| MTBF at 85°C | 70,119 hrs (according to MIL calculation)  |

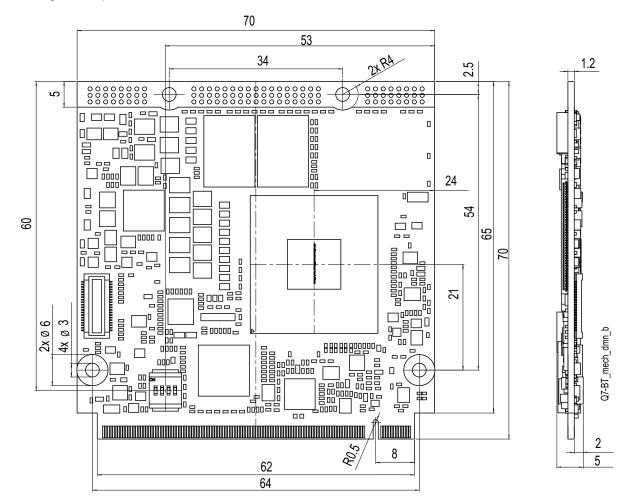

## 1.4.4 Mechanical

Figure 1-3 provides the mechanical dimensions of the Q7-BT.

Figure 1-3: Mechanical dimensions (top side)

ADLINK strongly recommends plastic spacers instead of metal spacers for mounting the board. Metal spacers create the possibilities of short circuits with the components located around the mounting holes, which can ruin the board.

## 1.4.5 **Power**

Table 1-5 provides the power requirements for this module under certain load configurations.

Table 1-5: Power Supply Requirements

| Parameter                               | 10W, E3845 SoC<br>Characteristics | 7W, E3826 SoC<br>Characteristics | 5W, E3815 SoC<br>Characteristics |

|-----------------------------------------|-----------------------------------|----------------------------------|----------------------------------|

| Input Type                              | Regulated DC voltage              | Regulated DC voltage             | Regulated DC voltage             |

| In-rush<br>Peak Current and<br>Duration | 5V / 1.75A (8.75W)                | 5V / 1.60A (8.00W)               | 5V / 1.05A (5.25W)               |

| Typical Idle Current and Power          | 5V / 0.86A (4.30W)                | 5V / 0.79A (3.95W)               | 5V / 0.62A (3.10W)               |

| BIT<br>Current and Power                | 5V / 2.71A (13.55W)               | 5V / 1.70A (8.95W)               | 5V / 1.20A (6.00W)               |

## Operating configurations:

- ▶ In-rush operating configuration Windows 8.1

- ▶ Idle operating configuration Windows 8.1

- ▶ BIT (Burn-In Test) operating configuration Windows 8.1; Intel TAT tool

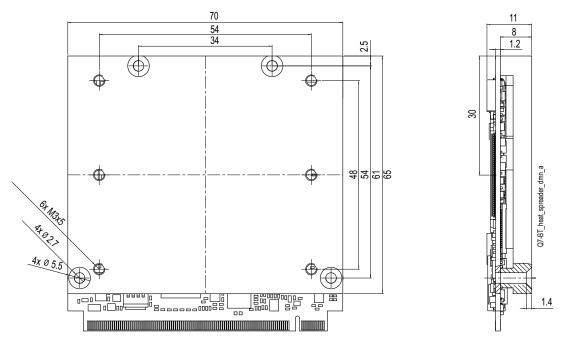

## 1.4.6 Cooling

The Q7-BT is designed to operate at its maximum CPU speeds of 1.46GHz and 1.91GHz and requires a thermal solution to cool the SoC. ADLINK offers a heat spreader as one part of the cooling solution. Refer to Figure 1-5 for diagram of heat spreader dimensions.

.

The Q7-BT supports two separate heat spreaders—one for board revision A2 and one for board revision A3. The two versions of the heat spreader require different order numbers, respectively.

The heat spreader plate requires another form of cooling, such as a heatsink with a fan. A heat spreader plate is not a complete thermal solution for the Q7-BT.

The overall system design must keep the ICs within their operating temperature specifications.

Figure 1-4: Heat Spreader mounting dimensions (top side)

## 1.5 Getting Started

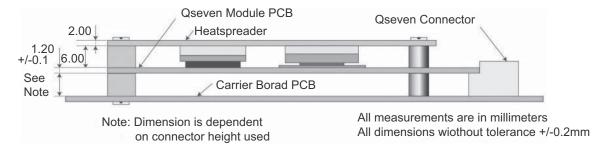

Mount the Q7-BT to the carrier as illustrated in Figure 1-5, which provides a profile view of the module mounted to the carrier with dimensions.

Figure 1-5: Qseven module mounting dimensions (profile)

ADLINK strongly recommends plastic spacers instead of metal spacers for mounting the board. Metal spacers create the possibilities of short circuits with the components located around the mounting holes, which can ruin the board

Be sure to observe the EMC security measures. Make sure you are always at the same potential as the module.

Never connect or disconnect peripherals like HDDs while the power supply is connected and switched on.

Use a commercial, high-quality display cable to connect an HDMI display. Connect a USB keyboard or mouse to the carrier. Use the SATA cable to connect the hard disk. Make sure that the pins match their counterparts correctly and are not twisted. If you plan to use additional peripherals, connect them to the appropriate headers or connectors on the carrier.

Connect a power supply to the power connector on the carrier and switch on the power.

Observe the minimum voltage values for the standard peripherals mentioned. For additional peripherals, make sure enough power is available. The system will not work if there is not enough supply current for all your devices.

The display shows the BIOS messages. If you want to change the standard BIOS settings, press the <DEL> key to enter the BIOS setup menus. See Chapter 4 for setup details.

If you need to load the BIOS default values, they can be automatically loaded at boot time.

The Q7-BT boots from CD drives, USB sticks, hard disks, or µSD-Cards. Provided that any of these is connected and contains a valid operating system image, the display then shows the boot screen of your operating system.

The Q7-BT needs adequate cooling measures depending on the desired operating temperature range. Using the board without cooling could damage the board permanently.

## 2 Hardware

This chapter describes the major integrated circuits (ICs) and interface connectors and headers on the module. The third section of this chapter further describes the major ICs on the board including a table of the SMBus slave device addresses on the board.

## 2.1 Major Components (ICs)

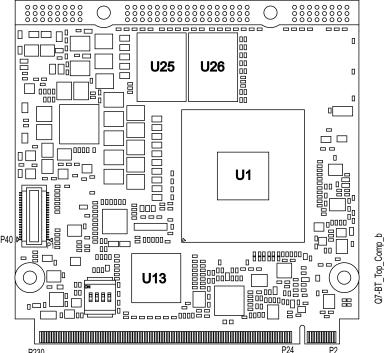

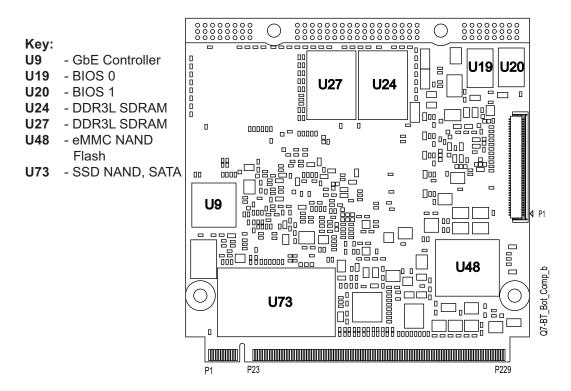

Table 2-1 lists the major integrated circuits on the Q7-BT, including a brief description of each IC. Figure 2-1 and Figure 2-2 show the locations of the major ICs.

Table 2-1:Major Integrated Circuit Descriptions and Functions

| Chip Type                                                              | Mfg.    | Model                                                                                                                                                                                              | Description                                                                                                            | Function                                                                                                    |

|------------------------------------------------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| CPU (U1)                                                               | Intel   | E3805 (dual core, 3W,<br>headless, 1.33GHz)<br>E3815 (single core, 5W,<br>1.46GHz)<br>E3825 (dual core, 6W,<br>1.33GHz)<br>E3826 (dual core, 7W,<br>1.46GHz)<br>E3845 (quad core, 10W,<br>1.91GHz) | Atom, 22nm SoC<br>(System on Chip) with<br>Intel 64 architecture                                                       | Integrates<br>Processor Core,<br>Graphics and<br>Memory Hub, and<br>I/O Hub                                 |

| Gb Ethernet<br>Controller (U9<br>on bottom<br>side; see<br>Figure 2-2) | Intel   | WGI210IT SLIXT                                                                                                                                                                                     | Single-port Gigabit<br>Ethernet controller                                                                             | Integrates GbE MAC, PHY, and SGMII/SerDes to enable 10T/ 100TX/1000T Ethernet signals using the PCIe x1 bus |

| BMC [Board<br>Management<br>Controller]<br>(U13)                       | Renesas | UDP78F0763GB-GAH-AX                                                                                                                                                                                | Micro controller for<br>board functions<br>including Watchdog<br>Timer and system<br>control and failure<br>protection | Controls dual<br>BIOS and SEMA<br>API through the<br>I <sup>2</sup> C bus                                   |

| SPI Flash<br>(U19 and U20<br>on bottom<br>side; see<br>Figure 2-2)     | Winbond | W25Q64FVSSIG TR                                                                                                                                                                                    | Serial Peripheral<br>Interface Flash<br>Memory chip (for<br>firmware)                                                  | Stores BIOS 0<br>and BIOS 1 in<br>Flash Memory                                                              |

Table 2-1:Major Integrated Circuit Descriptions and Functions (Continued)

| Chip Type                                                                                          | Mfg.               | Model                                                                                   | Description                                                                                                    | Function                                                              |

|----------------------------------------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| DDR3L<br>SDRAM<br>(U24, U25,<br>U26, U27 [U24<br>and U27 on<br>bottom side;<br>see<br>Figure 2-2]) | Micron             | MT41K128M16     (1GB board configuration)     MT41K256M16     (2GB board configuration) | On-board DDR3L,<br>1.35V, 4Gb,<br>32Mx16x8, non-ECC<br>System Memory<br>• 4Gb, 4x 128Mx16<br>• 4Gb, 4x 256Mx16 | Provides<br>high-speed data<br>transfer                               |

|                                                                                                    |                    |                                                                                         | On-board DDR3L,<br>1.35V, 8Gb,<br>64Mx16x8, non-ECC<br>System Memory                                           |                                                                       |

|                                                                                                    | I'M<br>Intelligent | IM8G16D3FBBG-15EI<br>(4GB board configuration)                                          | • 8Gb, 4x 512Mx16                                                                                              |                                                                       |

| eMMC, NAND<br>Flash (U48 on<br>bottom side;<br>see<br>Figure 2-2)                                  | Micron             | MTFC8GLVEA-4M-IT                                                                        | MultiMediaCard<br>Controller and NAND<br>Flash Memory up to<br>64GB                                            | Provides<br>communication<br>and mass data<br>storage<br>capabilities |

| SATA NAND<br>SSD (U73 on<br>bottom side;<br>see<br>Figure 2-2)<br>[Optional]                       | Greenliant         | GLS85LS1008B                                                                            | Industrial-grade<br>soldered solid-state<br>storage module                                                     | Provides solid<br>state storage<br>through SATA 1<br>port             |

Key:

**U1** - CPU **U13** - BMC

U25 - DDR3L SDRAM

U26 - DDR3L SDRAM

Figure 2-1: Component Locations (Top Side)

Figure 2-2: Component Locations (Bottom Side)

## 2.2 Connectors, Switches, and LEDs

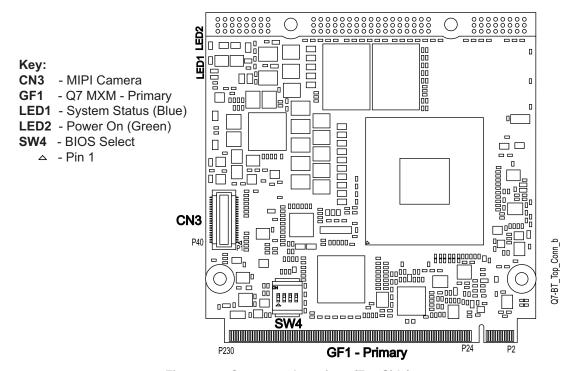

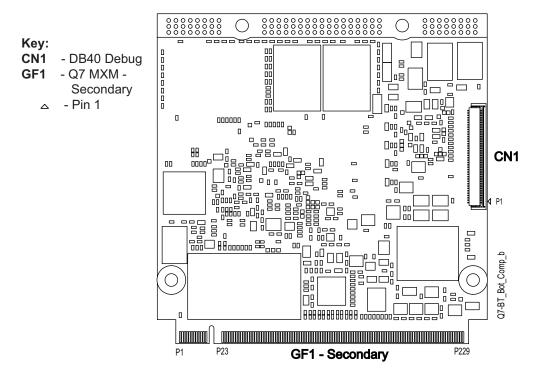

Table 2-2 describes the connectors, switches, and LEDs shown in Figure 2-3 and Figure 2-4.

**Board** Connector# Description Access CN1 40-pin, DB40 Front-Flip connector for debug card **Bottom** (Molex, 502790-4091) 40-pin, board-to-FPC connector for MIPI camera interface CN3 Top (Hirose, DF23C-40DS-0.5V) GF1 - Q7 Primary and Top/ 230-pin, MXM edge connector for Memory, Video, and I/O Secondary **Bottom** functions Blue LED indicating system status activities for HW Reset, LED1 Top SW Reset, Power Up, Power Down, Reset Button, and Power Button LED2 Top Green LED for Power On

**Table 2-2: Module Connector Description**

Table 2-2: Module Connector Description (Continued)

| Connector# | Board<br>Access | Description                                                                                                                                                                                                                                                                                                                                                                 |  |

|------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SW4        | Тор             | <ul> <li>4-pin dip switch for the following BIOS control functions. (Diptronics, DHNF-04-T-Q-T/R)</li> <li>Pin 1 = Loading BIOS setup defaults at Boot Up (OFF - default)</li> <li>Pin 2 = Enabling WDT (OFF - default)</li> <li>Pin 3 = Selecting BIOS (OFF - Fail-safe BIOS1; ON - Standard BIOS0 [default])</li> <li>Note: The BIOS_DISABLE# signal on the Q7</li> </ul> |  |

|            |                 | connector must be pulled low before Pin 3 can be used to select Fail-Safe BIOS1.                                                                                                                                                                                                                                                                                            |  |

|            |                 | Pin 4 = Selecting 18/24 bit LVDS modes (OFF - 18bit [default]; ON - 24bit)                                                                                                                                                                                                                                                                                                  |  |

|            |                 | Switch Default Settings  Switch Default Settings  Switch Default Settings                                                                                                                                                                                                                                                                                                   |  |

Figure 2-3: Connector Locations (Top Side)

Figure 2-4: Connector Locations (Bottom Side)

## 2.3 Component Features

This section further describes the supported features of the Q7-BT major on-board components.

## 2.3.1 CPU

The Q7-BT product family offers multiple versions of the Intel Atom E3800 Series CPU, System-on-Chip (SoC): the E3815 (Single Core), the E3825 (Dual Core), the E3826 (Dual Core), and the E3845 (Quad Core). E3800 CPUs feature the Intel 64 Architecture and are manufactured based on Intel's 22-nanometer technology. Refer to the E3800 data sheet at the Intel website.

## 2.3.2 Memory

The Q7-BT employs one channel of 64-bit DDR3L on-board memory. Four SDRAM memory chips provide up to 16Gb of low-voltage non-ECC, unbuffered system memory. Refer to the SDRAM data sheets at the Micron and IM Intelligent websites. Depending on the SDRAM chips featured on the module, the following total SDRAM capacities are supported:

- ▶ 4x 128M16 = 1 GB

- ▶ 4x 256M16 = 2 GB

- ► 4x 512M16 = 4 GB

## 2.3.3 eMMC NAND Flash

The module supports an optional, on-board eMMC (Multi-Media Card) NAND chip with capacity up to 64GB. The data signals are routed from the NAND chip through the SDIO pins on the Q7 connector. Refer to the MTFC8GLDEA-4M-IT NAND Flash data sheet at the Micron website.

## 2.3.4 SATA SSD (Solid State Drive)

The Q7-BT features an optional SATA SSD, soldered directly to the board and routed through the SATA1 port. For more information, refer to the SSD data sheet at the Greenliant website.

## 2.3.5 SMBus Slave Addresses

Figure 2-1 lists the corresponding slave addresses of the devices on the SMBus.

Table 2-1: SMBus Slave Addresses

| Address (HEX)     | Function   | Device    |

|-------------------|------------|-----------|

| (50)              | BMC/SEMA   | ВМС       |

| (6A)              | DP to LVDS | RTD2136R  |

| (2C) <sup>7</sup> | USB-Hub    | USB2514Bi |

This section provides descriptions of the interfaces and signals within the Q7-BT P-S (Primary-Secondary) Qseven connector. Refer to the Qseven specification at:

http://www.sget.org/standards/qseven.html for complete definitions of all the Qseven interfaces.

The Q7-BT P-S (Primary-Secondary) Qseven connector provides the following interfaces:

- ▶ LVDS

- ► HDMI

- ► Camera MIPI-CSI

- ► Audio

- ▶ PCI Express (PCIe)

- ▶ Gb Ethernet

- ▶ USB 2.0

- ▶ USB 3.0

- ► SATA

- ▶ 12C

- SPI

- ► Serial UART

- ▶ SD/SDIO

- ▶ eMMC

- ▶ Debug

ADLINK Technology, Inc. only supports the features/ options tested and listed in this manual. The main chips used in the Q7-BT may provide more features or options than are listed for the Q7-BT, but some of these features or options are not supported on the module and will not function as specified in the chip documentation.

#### 3.1 18/24-Bit LVDS LCD

The LVDS interface is connected to the DDI0 interface of the CPU, while the translations of the DDI signals are made by a DisplayPort™-to-LVDS converter. The Realtek RTD2136R-CG, DisplayPort-to-LVDS converter receives one lane of DisplayPort signals and generates one port of LVDS output. The interface supports resolutions up to 1920x1200 at 60Hz (for 18-bit color depth.) The backlight enable, display enable, and PWMOUT functions originate from the BMC and the CPU and can be controlled from the BIOS setup utility.

## 3.2 HDMI or Display Port (DP)

The default setup defines the DDI1 port as HDMI (TMDS) or DP and provides the following features:

- ▶ 1 Clock pair

- 3 Data pairs

- ▶ Service signals

- ▶ HDMI resolutions up to 1920x1200 at 60Hz

- ▶ DP resolutions up to 2560x1600 at 60Hz

Select between DisplayPort and HDMI in the Advanced Graphics menu of the BIOS setup utility. The HDMI interface is compliant with the HDMI 1.4 specification.

#### 3.3 Camera MIPI-CSI

The Q7-BT provides a 40-pin, on-board MIPI-CSI 2.0 (serial) camera connector with two clock lanes and five data lanes supporting up to 800 Mbit/s of actual pixels.

## 3.4 Audio (HDA)

The CPU provides an HDA controller, which communicates with internal or external CODECs over the Intel HDA serial link. HDA signals are brought out through pins 59, 61, 63, 65, 67 on the Qseven connector.

One audio link can be routed through the DDI1 interface and one link can be routed to the audio CODEC on the base board. Consequently, audio over DisplayPort/HDMI and the use of an audio CODEC can be implemented at the same time.

## 3.5 PCI Express (PCIe)

The CPU features four PCle x1 ports, and the Q7-BT module uses three of them for the PCle interface and one of them for the Gigabit Ethernet interface. The PCle interface supports the PCle Base Specification 2.0 with a maximum signal rate of 5 GT/s and can be configured to support PCle edge cards or Express Cards.

## 3.6 Gigabit Ethernet

The on-board Intel I210IT Ethernet controller uses PCIe x1 (v2.1) bus signals from the CPU to enable 10T/100TX/1000T operation through integrated MAC, PHY, and SGMII/SerDes interfaces.

#### 3.7 USB Ports

The USB interface provides five USB 2.0 host ports, one USB 2.0 client port, and one USB 3.0 host port.

For the USB 3.0 port to support a full super-speed connector, it must use one of the USB 2.0 host ports, leaving four 2.0 ports available.

#### **3.8 SATA**

The SATA interface provides two ports through the SATA0 and SATA1 pins on the Q7-BT connector. The interface supports 1.5Gb/s and 3.0Gb/s. One of the SATA ports is shared with the PCIe Mini Card socket on the baseboard.

#### 3.9 I2C Bus

The Q7-BT provides two interfaces through the I2C bus for General Purpose and LCD video with operating speeds up to 400kHz. All I2C interfaces have 3.3V pull ups with 2.2k resistors.

#### 3.10 SPI

The CPU implements an SPI controller, which supports two SPI Flash devices on the module for BIOS storage.

## 3.11 Serial (UART)

The Q7-BT provides one serial interface: one high-speed, 4-wire port with TX/RX and RTS#/CTS# signals.

#### 3.12 SD/SDIO Interface

Four parallel data lines comprise the SD/SDIO interface, supporting SD Card sockets.

## 3.13 eMMC Interface

The Q7-BT provides one 8-bit eMMC interface port, brought out from the CPU through the SDIO pins on the Qseven connector. If the optional eMMC NAND chip is present on the module, the eMMC interface will not be available for the baseboard on the Qseven connector.

## 3.14 LPC Debug Interface

A 40-pin, front flip, DB40 connector allows access to the system to debug and update the BIOS, BMC, and OS code. (Refer to "Debug (DB40) Connector Signals" on page 25.)

#### 3.15 MIPI CSI Camera Interface

A 40-pin, board-to-FPC connector provides MCSI signals for MIPI CSI camera devices. (Refer to "MIPI CSI Camera Connector Signals" on page 26.)

# 3.16 Qseven Interface Signals

Table 3-1 provides the pin signals for the Qseven connector. Refer to the Qseven specification at <a href="http://www.sget.org/standards/qseven.html">http://www.sget.org/standards/qseven.html</a> for further definitions of the Qseven signals.

Table 3-1: Q7 Interface (GF1) Signal Descriptions

| Pin# | Primary (Top Side)                                                                                                                                                                                                                                                                                                                                                                           | Pin# | Secondary (Bottom Side)                                                                                                                                                                                                                      |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | GND                                                                                                                                                                                                                                                                                                                                                                                          | 2    | GND                                                                                                                                                                                                                                          |

| 3    | GBE_MDI3- (Media Dependent Interface (MDI) differential pair 3. The MDI can operate in 1000, 100, and 10Mbit/sec modes. This signal pair is only used for 1000Mbit/sec Gigabit Ethernet mode.)                                                                                                                                                                                               | 4    | GBE_MDI2- (Media Dependent Interface (MDI) differential pair 2. The MDI can operate in 1000, 100, and 10Mbit/sec modes. This signal pair is only used for 1000Mbit/sec Gigabit Ethernet mode.)                                               |

| 5    | GBE_MDI3+ (Media Dependent Interface (MDI) differential pair 3. The MDI can operate in 1000, 100, and 10Mbit/sec modes. This signal pair is only used for 1000Mbit/sec Gigabit Ethernet mode.)                                                                                                                                                                                               | 6    | GBE_MDI2+ (Media Dependent Interface (MDI) differential pair 2. The MDI can operate in 1000, 100, and 10Mbit/sec modes. This signal pair is only used for 1000Mbit/sec Gigabit Ethernet mode.)                                               |

| 7    | GBE_LINK100# (Ethernet controller 0 100Mbit/sec link indicator, active low.)                                                                                                                                                                                                                                                                                                                 | 8    | GBE_LINK1000# (Ethernet controller 0 1000Mbit/sec link indicator, active low.)                                                                                                                                                               |

| 9    | GBE_MDI1- (Media Dependent Interface (MDI) differential pair 1. The MDI can operate in 1000, 100, and 10Mbit/sec modes. This signal pair is used for all modes.)                                                                                                                                                                                                                             | 10   | GBE_MDI0- (Media Dependent Interface (MDI) differential pair 0. The MDI can operate in 1000, 100, and 10Mbit/sec modes. This signal pair is used for all modes.)                                                                             |

| 11   | GBE_MDI1+ (Media Dependent Interface (MDI) differential pair 1. The MDI can operate in 1000, 100, and 10Mbit/sec modes. This signal pair is used for all modes.)                                                                                                                                                                                                                             | 12   | GBE_MDI0+ (Media Dependent Interface (MDI) differential pair 0. The MDI can operate in 1000, 100, and 10Mbit/sec modes. This signal pair is used for all modes.)                                                                             |

| 13   | GBE_LINK# (Ethernet controller 0 link indicator, active low.)                                                                                                                                                                                                                                                                                                                                | 14   | GBE_ACT# (Ethernet controller 0 activity indicator, active low.)                                                                                                                                                                             |

| 15   | GBE_CTREF (Reference voltage for carrier board Ethernet channel 0 magnetics center tap. The reference voltage is determined by the requirements of the module's PHY and may be as low as 0V and as high as 3.3V. The reference voltage output should be current limited on the module. In a case in which the reference is shorted to ground, the current must be limited to 250mA or less.) | 16   | SUS_S5# (S5 State: This signal indicates S4 or S5 [Soft Off] state.)                                                                                                                                                                         |

| 17   | WAKE# (External system wake event.<br>This may be driven active low by external<br>circuitry to signal an external wake-up<br>event.)                                                                                                                                                                                                                                                        | 18   | SUS_S3# (S3 State: This signal shuts off power to all runtime system components that are not maintained during S3 (Suspend to Ram), S4 or S5 states.  The signal SUS_S3# is necessary in order to support the optional S3 cold power state.) |

| 19   | SUS_STAT# (Suspend Status: indicates that the system will be entering a low power state soon.)                                                                                                                                                                                                                                                                                               | 20   | PWRBTN# (Power Button: Low active power button input. This signal is triggered on the falling edge.)                                                                                                                                         |

Table 3-1: Q7 Interface (GF1) Signal Descriptions (Continued)

| Pin# | Primary (Top Side)                                                                                                                                                                                                       | Pin# | Socondary (Bottom Side)                                                                                                                                             |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | , , , ,                                                                                                                                                                                                                  |      | Secondary (Bottom Side)                                                                                                                                             |

| 21   | SLP_BTN# (Sleep button. Low active signal used by the ACPI operating system to transition the system into sleep state or to wake it up again. This signal is                                                             | 22   | LID_BTN# (LID button. Low active signal used by the ACPI operating system to detect a LID switch and to bring system into sleep state or to wake it up again. Open/ |

| 22   | triggered on falling edge.) GND                                                                                                                                                                                          | 24   | Close state may be software configurable.) GND                                                                                                                      |

| 23   | KEY                                                                                                                                                                                                                      | 24   | KEY                                                                                                                                                                 |

| 25   | GND                                                                                                                                                                                                                      | 26   |                                                                                                                                                                     |

| 25   |                                                                                                                                                                                                                          |      | PWGIN                                                                                                                                                               |

| 27   | BATLOW# (Battery low input. This signal may be driven active low by external circuitry to signal that the system battery is low or may be used to signal some other external battery management event.)                  | 28   | RSTBTN# (High active input for the Qseven module indicates that all power rails located on the carrier board are ready for use.)                                    |

| 29   | SATA0_TX+ (Serial ATA channel 0, Transmit Output differential pair.)                                                                                                                                                     | 30   | SATA1_TX+ (Serial ATA channel 1, Transmit Output differential pair; not available if optional SATA SSD is installed)                                                |

| 31   | SATA0_TX- (Serial ATA channel 0,<br>Transmit Output differential pair.)                                                                                                                                                  | 32   | SATA1_TX-<br>(Serial ATA channel 1, Transmit Output<br>differential pair; not available if optional<br>SATA SSD is installed)                                       |

| 33   | SATA_ACT# (Serial ATA Led. Open collector output pin driven during SATA command activity.)                                                                                                                               | 34   | GND                                                                                                                                                                 |

| 35   | SATA0_RX+ (Serial ATA channel 0, Receive Input differential pair.)                                                                                                                                                       | 36   | SATA1_RX+ (not available if optional SATA SSD is installed)                                                                                                         |

| 37   | SATA0_RX- (Serial ATA channel 0, Receive Input differential pair.)                                                                                                                                                       | 38   | SATA1_RX-<br>(Serial ATA channel 1, Receive Input<br>differential pair; not available if optional<br>SATA SSD is installed)                                         |

| 39   | GND                                                                                                                                                                                                                      | 40   | GND                                                                                                                                                                 |

| 41   | BIOS_DISABLE# (Module BIOS disable input signal. Pull low to disable module's on-board BIOS. Allows off-module BIOS implementations.)                                                                                    | 42   | SDIO_CLK# (SDIO Clock. With each cycle of this signal a one-bit transfer on the command and each data line occurs. This signal has maximum frequency of 48 MHz.)    |

| 43   | SDIO_CD# (SDIO Card Detect. This signal indicates when a SDIO/MMC card is present.)                                                                                                                                      | 44   | SDIO_LED (SDIO LED. Used to drive an external LED to indicate when transfers occur on the bus.)                                                                     |

| 45   | SDIO_CMD (SDIO Command/Response. This signal is used for card initialization and for command transfers. During initialization mode this signal is open drain. During command transfer this signal is in push-pull mode.) | 46   | SDIO_WP (SDIO Write Protect. This signal denotes the state of the write-protect tab on SD cards.)                                                                   |

| 47   | SDIO_PWR# (SDIO Power Enable. This signal is used to enable the power being supplied to a SD/MMC card device.)                                                                                                           | 48   | SDIO_DAT1 (These signals operate in push-pull mode.)                                                                                                                |

| 49   | SDIO_DAT0 (These signals operate in push-pull mode.)                                                                                                                                                                     | 50   | SDIO_DAT3 (These signals operate in push-pull mode.)                                                                                                                |

| 51   | SDIO_DAT2 (These signals operate in push-pull mode.)                                                                                                                                                                     | 52   | Not Connected                                                                                                                                                       |

| 53   | Not Connected                                                                                                                                                                                                            | 54   | Not Connected                                                                                                                                                       |

Table 3-1: Q7 Interface (GF1) Signal Descriptions (Continued)

| Pin# | Primary (Top Side)                                                                                                                                                            | Pin# | Secondary (Bottom Side)                                                                                                                                                  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 55   | Not Connected                                                                                                                                                                 | 56   | RSVD                                                                                                                                                                     |

| 57   | GND                                                                                                                                                                           | 58   | GND                                                                                                                                                                      |

| 59   | HDA_SYNC (Serial Bus Audio Synchronization.)                                                                                                                                  | 60   | SMB_CLK (Clock line of System Management Bus.)                                                                                                                           |

| 61   | HDA_RST#(HD Audio/AC'97 Codec Reset.)                                                                                                                                         | 62   | SMB_DAT (Data line of System Management Bus.)                                                                                                                            |

| 63   | HDA_BITCLK (HD Audio/AC'97 24 MHz<br>Serial Bit Clock from Codec)                                                                                                             | 64   | SMB_ALERT# (System Management Bus<br>Alert input. This signal may be driven low by<br>SMB devices to signal an event on the SM<br>Bus.)                                  |

| 65   | HDA_SDI (HD Audio/AC'97 Serial Data Input from Codec)                                                                                                                         | 66   | GPO_I2C_CLK (General Purpose I <sup>2</sup> C bus #0 clock line.)                                                                                                        |

| 67   | HDA_SDO (HD Audio/AC'97 Serial Data Output to Codec)                                                                                                                          | 68   | GPO_I2C_DAT (General Purpose I²C bus #0 data line.)                                                                                                                      |

| 69   | THRM# (Thermal Alarm active low signal generated by the external hardware to indicate an over temperature situation. This signal can be used to initiate thermal throttling.) | 70   | WDTRIG# (Watchdog trigger signal. This signal restarts the watchdog timer of the Qseven module on the falling edge of a low active pulse.)                               |

| 71   | THRMTRIP# (Thermal Trip indicates an overheating condition of the processor. If 'THRMTRIP#' goes active, the system immediately transitions to the S5 State [Soft Off].)      | 72   | WDOUT (Watchdog event indicator. High active output used for signaling a missing watchdog trigger. Will be deasserted by software, system reset or a system power down.) |

| 73   | GND                                                                                                                                                                           | 74   | GND                                                                                                                                                                      |

| 75   | USB_SSTX0- [USB 3.0] (Multiplexed with transmit signal differential pairs for the Superspeed USB data path.)                                                                  | 76   | USB_SSRX0- [USB 3.0] (Receive signal differential pair for the Superspeed USB data path.)                                                                                |

| 77   | USB_SSTX0+ [USB 3.0] (Multiplexed with transmit signal differential pairs for the Superspeed USB data path.)                                                                  | 78   | USB_SSRX0+ [USB 3.0] (Receive signal differential pair for the Superspeed USB data path.)                                                                                |

| 79   | USB_6_7_OC# (Over current detect input 4. This pin is used to monitor the USB power over current of the USB Ports 6 and 7.)                                                   | 80   | USB_4_5_OC# (Over current detect input 3. This pin is used to monitor the USB power over current of the USB Ports 4 and 5.)                                              |

| 81   | USB_P5- (Universal Serial Bus Port 5 differential pair.)                                                                                                                      | 82   | USB_P4- (Universal Serial Bus Port 4 differential pair.)                                                                                                                 |

| 83   | USB_P5+ (Universal Serial Bus Port 5 differential pair.)                                                                                                                      | 84   | USB_P4+ (Universal Serial Bus Port 4 differential pair.)                                                                                                                 |

| 85   | USB_2_3_OC# (Over current detect input 2. This pin is used to monitor the USB power over current of the USB Ports 2 and 3.)                                                   | 86   | USB_0_1_OC# (Over current detect input 1. This pin is used to monitor the USB power over current of the USB Ports 0 and 1.)                                              |

| 87   | USB_P3- (Universal Serial Bus Port 3 differential pair.)                                                                                                                      | 88   | USB_P2- (Universal Serial Bus Port 2 differential pair.)                                                                                                                 |

| 89   | USB_P3+ (Universal Serial Bus Port 3 differential pair.)                                                                                                                      | 90   | USB_P2+ (Universal Serial Bus Port 2 differential pair.)                                                                                                                 |

Table 3-1: Q7 Interface (GF1) Signal Descriptions (Continued)

| Pin# | Primary (Top Side)                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Pin# | Secondary (Bottom Side)                                                                                                                                                                                                                                                     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 91   | USB_CC (USB Client Connect pin. If USB Port 1 is configured for client mode, then an externally connected USB host should set this signal to high-active in order to properly make the connection with the module's internal USB client controller. If the external USB host is disconnected, this signal should be set to low-active in order to inform the USB client controller that the external host has been disconnected. A level shifter/protection circuitry should be implemented on.) | 92   | USB_ID (USB ID pin. Configures the mode of the USB Port 1. If the signal is detected as being 'high active' the BIOS will automatically configure USB Port 1 as USB Client and enable USB Client support. This signal should be driven as OC signal by external circuitry.) |

| 93   | USB_OTG- (USB client)                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 94   | USB_P0- (Universal Serial Bus Port 0 differential pair.)                                                                                                                                                                                                                    |

| 95   | USB_OTG+(USB client)                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 96   | USB_P0+ (Universal Serial Bus Port 0 differential pair.)                                                                                                                                                                                                                    |

| 97   | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 98   | GND                                                                                                                                                                                                                                                                         |

| 99   | eDP0_TX0+ (option) / LVDS_A0+ (LVDS primary channel differential pair 0.  Embedded Display Port primary channel differential pair 0.)                                                                                                                                                                                                                                                                                                                                                            | 100  | LVDS_B0+ (LVDS secondary channel differential pair 0.)                                                                                                                                                                                                                      |

| 101  | eDP0_TX0- (option) / LVDS_A0-<br>(LVDS primary channel differential pair 0.<br>Embedded Display Port primary channel<br>differential pair 0.)                                                                                                                                                                                                                                                                                                                                                    | 102  | LVDS_B0- (LVDS secondary channel differential pair 0.)                                                                                                                                                                                                                      |

| 103  | eDP0_TX1+ (option) / LVDS_A1+ (LVDS primary channel differential pair 1.  Embedded Display Port primary channel differential pair 1.)                                                                                                                                                                                                                                                                                                                                                            | 104  | LVDS_B1+ (LVDS secondary channel differential pair 1.)                                                                                                                                                                                                                      |

| 105  | eDP0_TX1- (option) / LVDS_A1-<br>(LVDS primary channel differential pair 1.<br>Embedded Display Port primary channel<br>differential pair 1.)                                                                                                                                                                                                                                                                                                                                                    | 106  | LVDS_B1- (LVDS secondary channel differential pair 1.)                                                                                                                                                                                                                      |

| 107  | eDP0_TX2+ (option) / LVDS_A2+ (LVDS primary channel differential pair 2.  Embedded Display Port primary channel differential pair 2.)                                                                                                                                                                                                                                                                                                                                                            | 108  | LVDS_B2+ (LVDS secondary channel differential pair 2.)                                                                                                                                                                                                                      |

| 109  | eDP0_TX2- (option) / LVDS_A2-<br>(LVDS primary channel differential pair 2.<br>Embedded Display Port primary channel<br>differential pair 2.)                                                                                                                                                                                                                                                                                                                                                    | 110  | LVDS_B2- (LVDS secondary channel differential pair 2.)                                                                                                                                                                                                                      |

| 111  | LVDS_PPEN (Controls panel power enable.)                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 112  | LVDS_BLEN (Controls panel backlight enable.)                                                                                                                                                                                                                                |

| 113  | eDP0_TX3+ (option) / LVDS_A3+ (LVDS primary channel differential pair 3.  Embedded Display Port primary channel differential pair 3.)                                                                                                                                                                                                                                                                                                                                                            | 114  | LVDS_B3+ (LVDS secondary channel differential pair 3.)                                                                                                                                                                                                                      |

Table 3-1: Q7 Interface (GF1) Signal Descriptions (Continued)

| Pin# | Primary (Top Side)                                                                                                      | Pin# | Secondary (Bottom Side)                                                                                              |

|------|-------------------------------------------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------|

| 115  | eDP0_TX3- (option) / LVDS_A3-<br>(LVDS primary channel differential pair 3.                                             | 116  | LVDS_B3- (LVDS secondary channel differential pair 3.)                                                               |

|      | Embedded Display Port primary channel differential pair 3.)                                                             |      |                                                                                                                      |

| 117  | GND                                                                                                                     | 118  | GND                                                                                                                  |

| 119  | eDP0_AUX+ (option) / LVDS_A_CLK+ (LVDS primary channel differential pair clock lines.                                   | 120  | LVDS_B_CLK+ (LVDS secondary channel differential pair clock lines.)                                                  |

|      | Embedded Display Port primary auxiliary channel.)                                                                       |      |                                                                                                                      |

| 121  | eDP0_AUX- (option) / LVDS_A_CLK-<br>(LVDS primary channel differential pair<br>clock lines.                             | 122  | LVDS_B_CLK- (LVDS secondary channel differential pair clock lines.)                                                  |

|      | Embedded Display Port primary auxiliary channel.)                                                                       |      |                                                                                                                      |

| 123  | LVDS_BLT_CTRL (Primary functionality is to control the panel backlight brightness via pulse width modulation [PWM].)    | 124  | GP_1-Wire Bus (General Purpose 1-Wire bus interface. Can be used for consumer electronics control bus (CEC) of HDMI) |

| 125  | LVDS_DID_DAT (Primary functionality DisplayID DDC data line used for LVDS flat panel detection.)                        | 126  | LVDS_BLC_DAT (Control data signal for external SSC clock chip.)                                                      |

| 127  | LVDS_DID_CLK (Primary functionality is DisplayID DDC clock line used for LVDS flat panel detection.)                    | 128  | LVDS_BLC_CLK (Control clock signal for external SSC clock chip.)                                                     |

| 129  | Not Connected                                                                                                           | 130  | Not Connected                                                                                                        |

| 131  | DP_LANE3+/TMDS_CLK+ (DisplayPort differential pair lines lane 3, shared with TMDS differential pair clock lines.)       | 132  | Not Connected                                                                                                        |

| 133  | DP_LANE3-/TMDS_CLK- (DisplayPort differential pair lines lane 3, shared with TMDS differential pair clock lines.)       | 134  | Not Connected                                                                                                        |

| 135  | GND                                                                                                                     | 136  | GND                                                                                                                  |

| 137  | DP_LANE1+/TMDS_LANE1+ (DisplayPort differential pair lines lane 1, shared with TMDS differential pair lines lane 1.)    | 138  | DDI1_AUX+ (Auxiliary channel used for link management and device control. Differential pair lines.)                  |

| 139  | DP_LANE1-/TMDS_LANE1-<br>(DisplayPort differential pair lines lane 1, shared with TMDS differential pair lines lane 1.) | 140  | DDI1_AUX- (Auxiliary channel used for link management and device control. Differential pair lines.)                  |

| 141  | GND                                                                                                                     | 142  | GND                                                                                                                  |

| 143  | DP_LANE2+/TMDS_LANE0+ (DisplayPort differential pair lines lane 2, shared with TMDS differential pair lines lane 0.)    | 144  | Not Connected                                                                                                        |

| 145  | DP_LANE2-/TMDS_LANE0-<br>(DisplayPort differential pair lines lane 2, shared with TMDS differential pair lines lane 0.) | 146  | Not Connected                                                                                                        |

Table 3-1: Q7 Interface (GF1) Signal Descriptions (Continued)

| Pin# | Primary (Top Side)                                                                                                            | Pin# | Secondary (Bottom Side)                                                                                                                                                                                |